Built-in and calibrated jitter source allow accurate jitter tolerance testing of receivers. Memory buses, such as fully buffered DIMM2Īutomated jitter tolerance characterizationĪccurate characterization is achieved with clean signals from the pattern generator, which features exceptionally low jitter and extremely fast transition times.

PCI Express® See Measurement Solution Example: PCIe 3.0 Receiver Test.

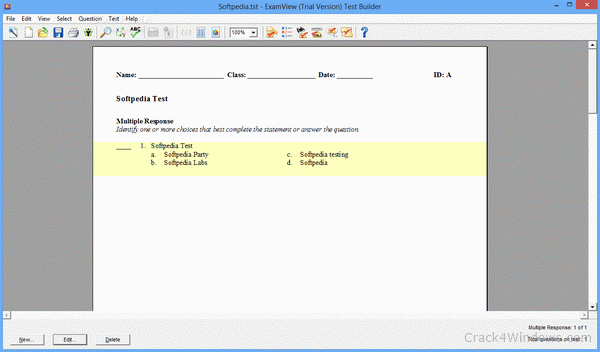

Multiple Choice Quiz Maker Serial serial#

It can characterize a receiver’s jitter tolerance and is designed to prove compliance to today’s most popular serial bus standards, such as: It is the ideal choice for R&D and validation teams characterizing and stressing chips and transceiver modules that have serial I/O ports up to 7 Gb/s, 12.5Gb/s or 14.2 Gb/s. The J-BERT N4903B high-performance serial BERT provides the most complete jitter tolerance test for embedded and forward clocked devices.

Option to extended data rate to 14.2 Gb/s for pattern generator.

Multiple Choice Quiz Maker Serial generator#

0 kommentar(er)

0 kommentar(er)